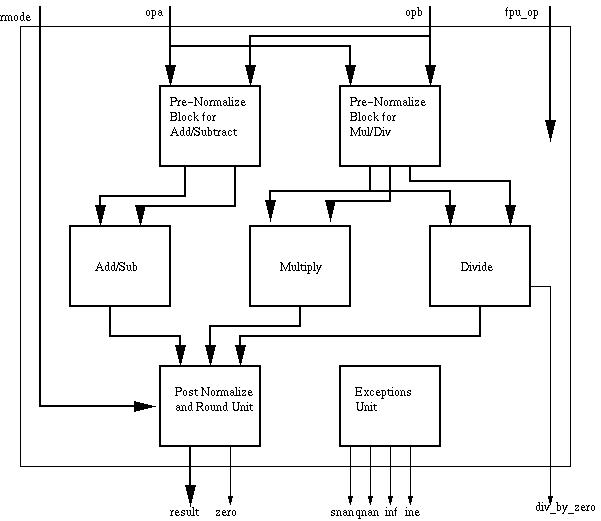

Design of FPGA based 32-bit Floating Point Arithmetic Unit and verification of its VHDL code using MATLAB

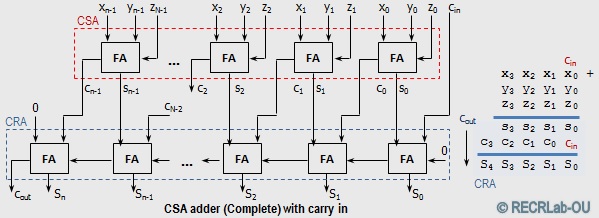

Figure 2 from VHDL implementation of self-timed 32-bit floating point multiplier with carry look ahead adder | Semantic Scholar

PPT - A CAD Tool for Scalable Floating Point Adder Design and Generation Using C++/VHDL PowerPoint Presentation - ID:4714007

GitHub - ahirsharan/32-Bit-Floating-Point-Adder: Verilog Implementation of 32-bit Floating Point Adder

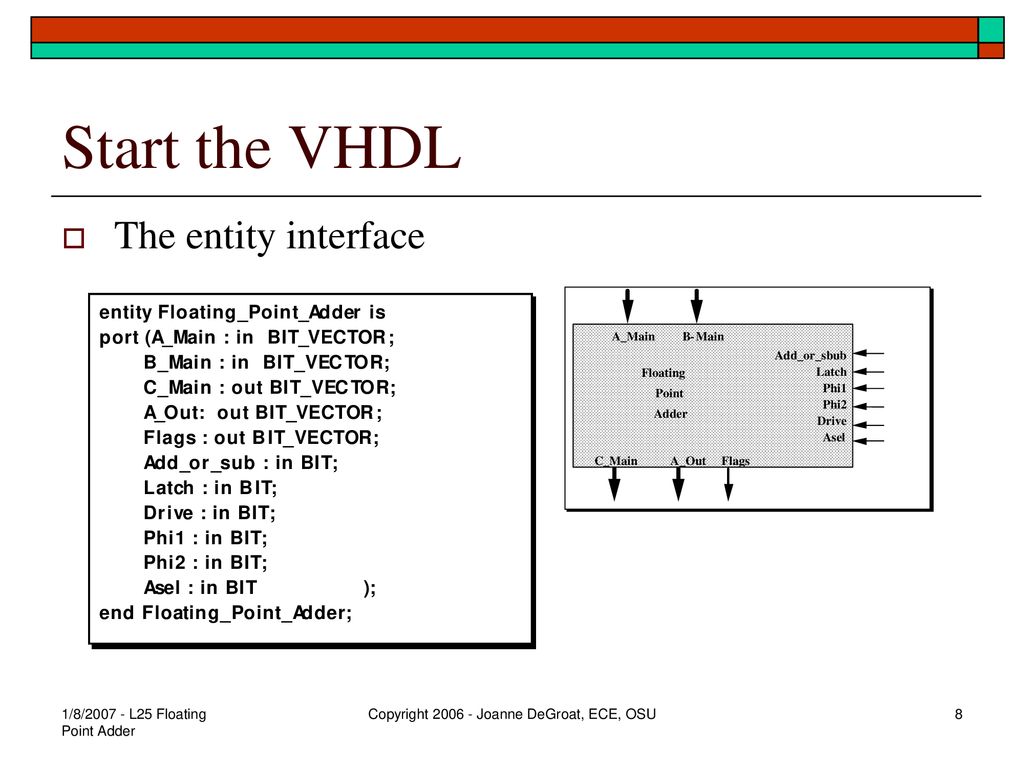

Design of Floating Point Adder/Subtractor and Floating Point Multiplier for FFT Architecture Using VHDL

GitHub - ahirsharan/32-Bit-Floating-Point-Adder: Verilog Implementation of 32-bit Floating Point Adder

![PDF] Review on Floating Point Adder and Converter Units Using VHDL | Semantic Scholar PDF] Review on Floating Point Adder and Converter Units Using VHDL | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/f1c8085c2de1844b64beeb7bf2d99089fd16070a/4-Figure8-1.png)

![PDF] Review on Floating Point Adder and Converter Units Using VHDL | Semantic Scholar PDF] Review on Floating Point Adder and Converter Units Using VHDL | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/f1c8085c2de1844b64beeb7bf2d99089fd16070a/3-Figure6-1.png)

![PDF] Review on Floating Point Adder and Converter Units Using VHDL | Semantic Scholar PDF] Review on Floating Point Adder and Converter Units Using VHDL | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/f1c8085c2de1844b64beeb7bf2d99089fd16070a/2-Figure2-1.png)